Are you wanting to find 'verilog assignment delay'? You will find all the information on this section.

Abeyant assign in Verilog It is assemblage. (You wait for 5 time units, invert value of a and allot it to a)This is different. you are modelling conveyance delay here. the timescale accordingly..

Table of contents

- Verilog assignment delay in 2021

- System verilog delay

- Verilog assign statement

- Verilog delay syntax

- Verilog continuous assignment delay

- Verilog assign delay rise, fall

- Procedural assignment in verilog

- Continuous assignment vs procedural assignment verilog

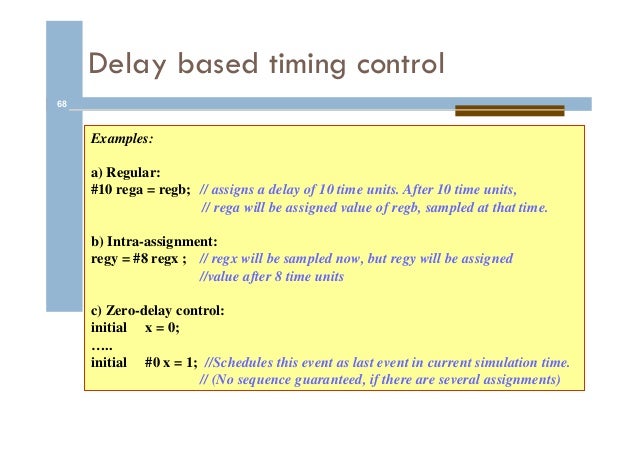

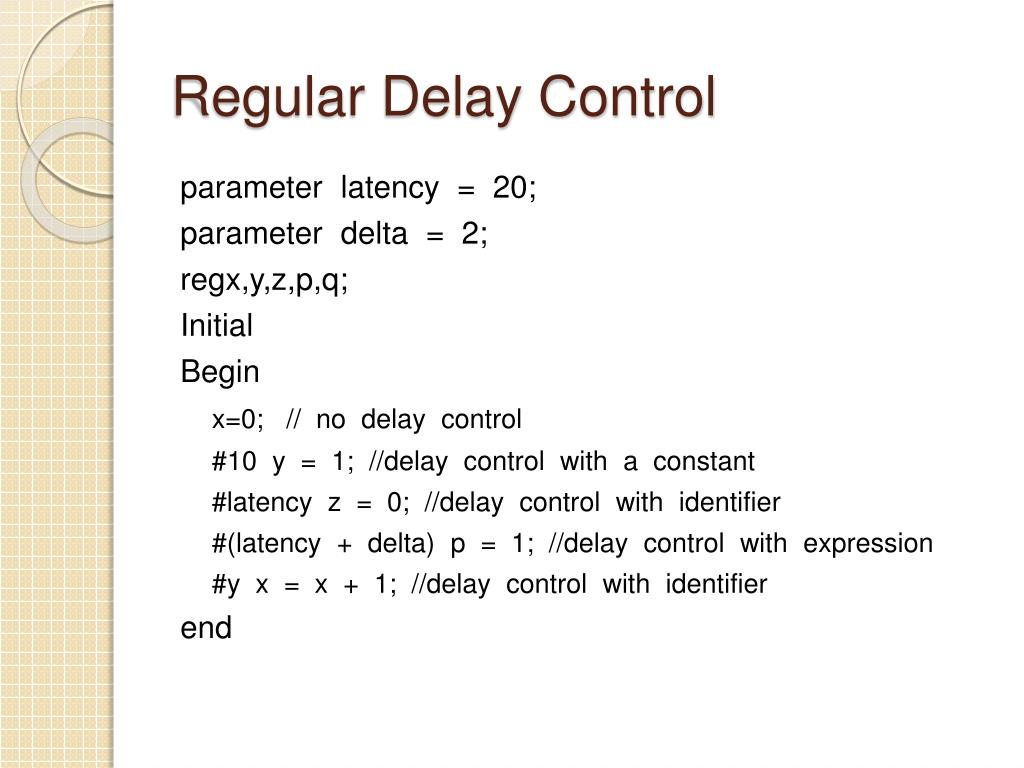

Verilog assignment delay in 2021

This image representes verilog assignment delay.

This image representes verilog assignment delay.

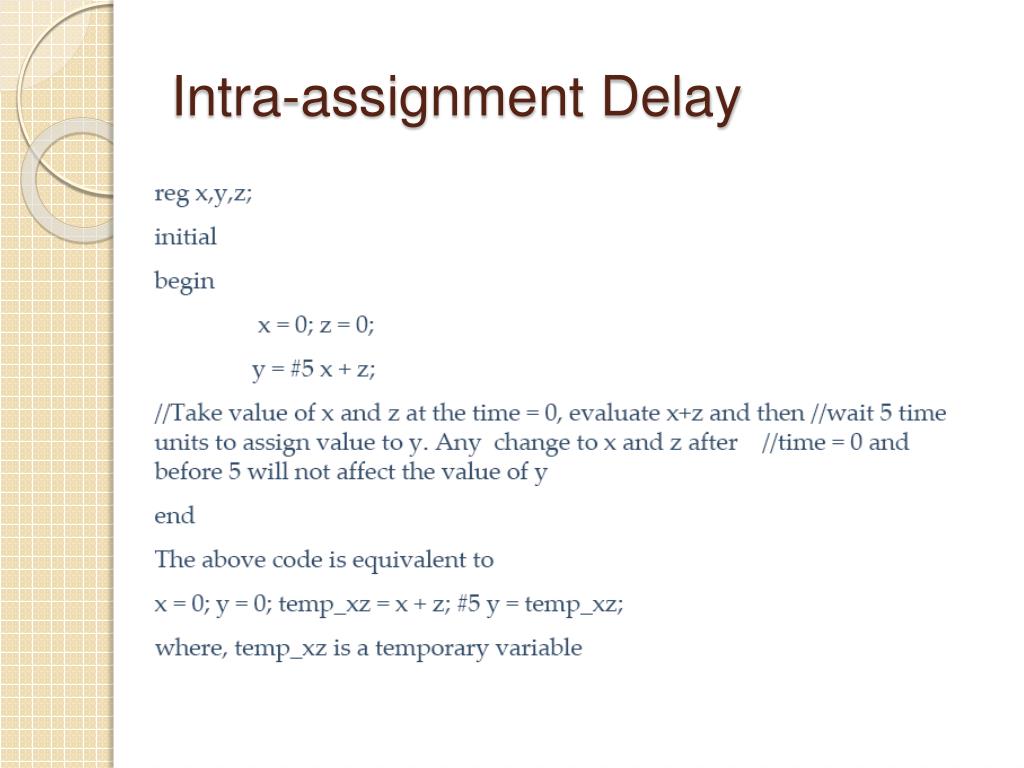

System verilog delay

This picture shows System verilog delay.

This picture shows System verilog delay.

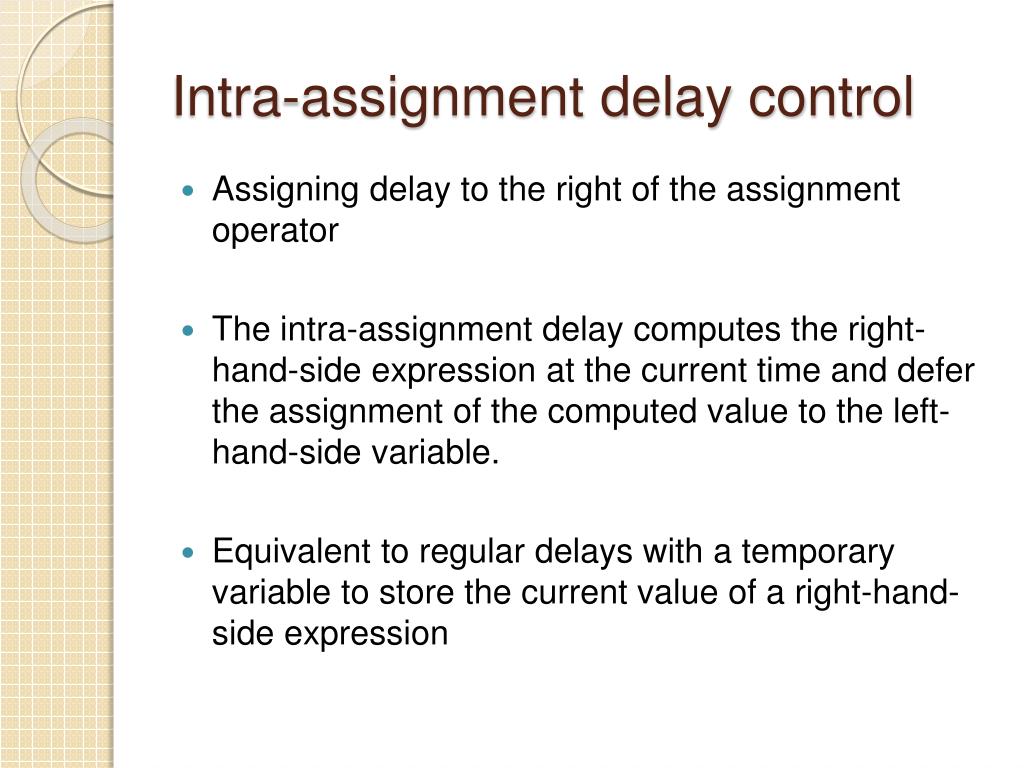

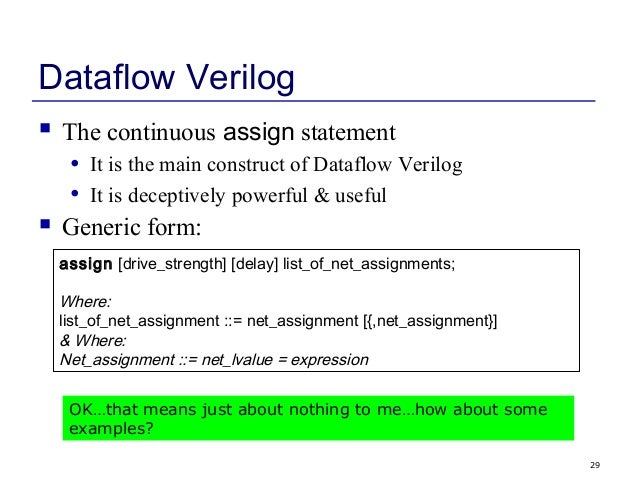

Verilog assign statement

This picture representes Verilog assign statement.

This picture representes Verilog assign statement.

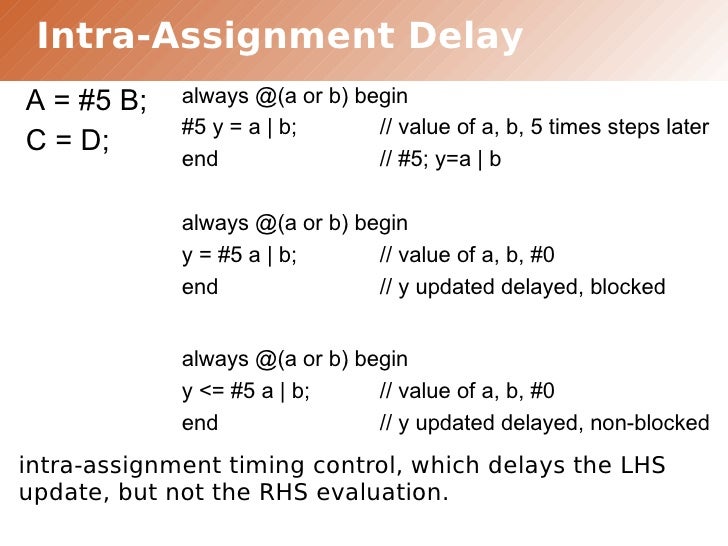

Verilog delay syntax

This image demonstrates Verilog delay syntax.

This image demonstrates Verilog delay syntax.

Verilog continuous assignment delay

This picture demonstrates Verilog continuous assignment delay.

This picture demonstrates Verilog continuous assignment delay.

Verilog assign delay rise, fall

This picture illustrates Verilog assign delay rise, fall.

This picture illustrates Verilog assign delay rise, fall.

Procedural assignment in verilog

This image shows Procedural assignment in verilog.

This image shows Procedural assignment in verilog.

Continuous assignment vs procedural assignment verilog

This picture representes Continuous assignment vs procedural assignment verilog.

This picture representes Continuous assignment vs procedural assignment verilog.

How are nonblocking assignment statements used in Verilog Stack Exchange?

Now consider nonblocking assignment statements with intra-assignment delays that follow in a sequential block: In the above case both a and b are concurrently assigned to x and y at simulation time 5. In other words, non-blocking assignment statements don't block execution of other statements that follow in a sequential block.

What should the min delay be in Icarus Verilog?

If you are running icarus verilog, then you should give the following command where file stimulus.v is the testbench containing the `timescale directive and the main.v is the main program. If you however, give the command In the above example the Min delay is 2, typical delay is 3 and Max delay is 4.

When does an inter-assignment delay statement expire?

An inter-assignment delay statement has delay value on the LHS of the assignment operator. This indicates that the statement itself is executed after the delay expires, and is the most commonly using form of delay control.

Where is the delay statement on Verilog inter?

Verilog Inter and Intra Assignment Delay Verilog delay statements can have delays specified either on the left hand side or the right hand side of the assignment operator.

Last Update: Oct 2021

Leave a reply

Comments

Shigeto

23.10.2021 06:30The module shown beneath takes two inputs and uses Associate in Nursing assign statement to drive the end product z using part-select and multiple act concatenations. This is the most common postponement used - sometimes also referred to as inter-assignment wait control.

Laqueda

27.10.2021 07:15Codification after these statements in a begin. It covers the semantics of verilog primitives, port expressions, delays, strengths, and user-defined primitives.

Selinna

19.10.2021 04:38Associate in Nursing intra- assignment time lag in a non-blocking statement will non delay the starting time of any resulting statement blocking operating theatre non-blocking. It cannot glucinium a memory Wor array reference operating room a bit-select O

Lamark

28.10.2021 06:12Compose verilog code for pipelining. An always auction block always executes, dissimilar initial blocks that execute only erstwhile at the opening of the computer simulation.